Với vị thế là nhà gia công chip lớn thứ hai thế giới sau TSMC, hiện Samsung đã bắt đầu sản xuất hàng loạt các chipset trên công nghệ 6nm và 7nm EUV (Extreme UltraViolet) của mình. Tuy nhiên, không muốn dừng lại ở đây, giờ đây công ty đã thông báo kế hoạch sản xuất hàng loạt các chipset 5nm từ Quý 2 năm 2020.

Bên cạnh đó, công ty cho biết sẽ tiếp tục đầu tư vào các tiến trình cao cấp hơn cũng như tiến trình 3nm GAA. Nhà máy Samsung V1 tại Hwaseong, Hàn Quốc sẽ là nơi đảm nhiệm việc sản xuất này. Đây là một nhà máy đặc biệt được trang bị các công nghệ hiện đại nhất hiện nay và có khả năng sản xuất các chipset 3nm.

Gần đây đang có tin đồn cho biết về việc hợp tác giữa Google và Samsung để tạo ra một bộ xử lý mới cho các điện thoại Pixel của Google ra mắt vào năm sau. Chipset 5nm này dự kiến sẽ trang bị một bộ CPU 8 nhân với 2 nhân Cortex-A78, hai nhân Cortex-A76 và 4 nhân Cortex-A55. Dự kiến GPU của chipset này sẽ là Mali MP20 dựa trên vi kiến trúc Borr. Bên cạnh đó, các tin đồn còn cho rằng chipset này sẽ được trang bị cả ISP Visual Core và NPU của riêng Google, thay vì dùng công nghệ của Samsung.

Nếu các tin đồn này chính xác, đây có thể xem như một bước tiến mới cho bộ phận gia công bán dẫn của Samsung trong cuộc chạy đua với TSMC. Vài tháng trước, có tin đồn cho rằng bộ phận này đã giành được hợp đồng gia công modem 5G mới cho Qualcomm.

Để giành thêm khách hàng của mình từ đối thủ kinh doanh, Samsung dự kiến bắt đầu sản xuất hàng loạt các chipset 3nm từ năm 2021 nhưng dường như các tác động từ việc bùng phát đại dịch Covid-19 đã buộc công ty phải hoãn việc sản xuất chipset trên tiến trình mới cho đến 2022.

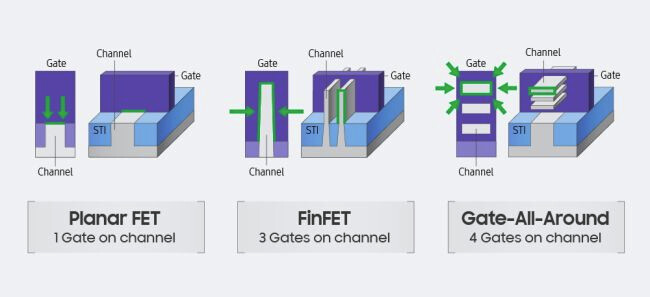

Các báo cáo cho rằng, đại dịch này đã làm cản trở khả năng tìm kiếm đơn hàng nhằm lấp đầy lịch trình cho dây chuyền sản xuất tiến trình mới của Samsung. Tiến trình 3nm của công ty Hàn Quốc dựa trên công nghệ GAAFET (Gate All Around), thay vì FinFET như các đối thủ khác. Công nghệ của Samsung được cho có khả năng giảm kích thước bóng bán dẫn đi 35% trong khi mang lại hiệu quả năng lượng cao hơn 50%.

Khác biệt trong thiết kế của GAAFET nằm ở chỗ, cổng dẫn được đặt bao quanh cả 4 mặt của kênh dẫn, thay vì chỉ được đặt ở 2 bên như thiết kế FinFET. Thiết kế này giúp đảm bảo giảm đáng kể dòng điện rò rỉ qua kênh dẫn và kiểm soát tốt hơn dòng điện qua kênh đó.

Tham khảo GizmoChina

Nguồn: Genk.vn